在8月下旬于美國矽谷舉行的年度Hot Chips大會上,Intel與Xilinx分享了晶片堆疊技術的最新進展.美國的一項研究專案旨在培育一個能以隨插即用的「小晶片(chiplet)」來設計半導體的生態系統;而在此同時,英特爾(Intel)和賽靈思(Xilinx)等廠商則是使用專有封裝技術,來讓自己的FPGA產品與競爭產品有所差異化。

在未來八個月,美國國防部高等研究計畫署(DARPA)的「CHIPS」(Common Heterogeneous Integration and Intellectual Property Reuse Strategies)專案,期望能定義與測試開放晶片介面(open chip interfaces),并在三年內讓許多公司運用該連結介面來打造各種復雜的零組件。

英特爾已經參與此項專案,其他廠商預計也會馬上跟進;這位x86架構的巨擘正在內部爭論是否要公開部份的嵌入式多晶片互連橋接技術(embedded multi-die interconnect bridge,EMIB),而在8月下旬于美國矽谷舉行的年度Hot Chips大會上,英特爾公布了目前EMIB技術的大部分細節。

有機基板(organic substrate)的多晶片模組(MCM)已經行之有年,除了相對較低密度的問題,有些供應商正在想辦法降低成本。臺積電率先推出了一種扇出型(fan out)晶圓級封裝,用來封裝蘋果(Apple)最新iPhone手機中的應用處理器及其記憶體,該技術提供比多晶片模組技術更大的密度,但用來連結處理器仍不夠力。

如同微軟,AMD的Epyc伺服器處理器不考慮采用相對昂貴的2.5D 堆疊技術,此處理器是由有機基板上的四顆裸晶(die)所組成。在Hot Chip大會上介紹該晶片的AMD代表Kevin Lepa表示:「較傳統的多晶片模組是較為人知的技術,成本更低…某些方面(效能)會有所犧牲,但我們認為這是可以接受的。」

一些人希望DARPA的研發專案能盡速解決復雜的技術與商業瓶頸,Xilinx的一位資深架構師即表示:「我們希望小晶片能變成更像是IP。」

在2014年,英特爾首先將其EMIB技術形容為功能媲美2.5D堆疊技術、但成本更低的方案,某部分是因為它只使用一部份的矽中介層(silicon-interposer)來連接任何尺寸的裸晶兩端。 Altera在被英特爾并購前嘗試過該技術,其現在出貨的高階Stratix FPGA使用EMIB來連結DRAM堆疊與收發器。

EMIB介面與CCIX進展

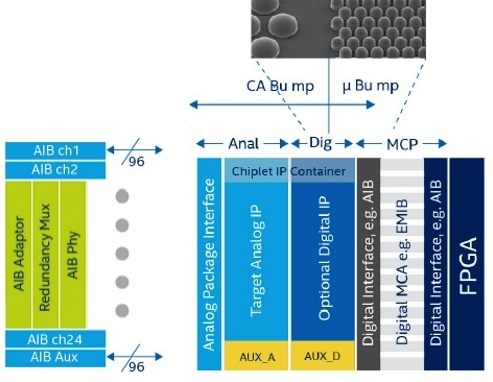

在Hot Chips大會上,英特爾介紹了兩種采用EMIB技術的介面,其一名為UIB,是以一種若非Samsung就是SK Hynix使用的DRAM堆疊Jedec連結標準為基礎;另外一個稱作AIB,是英特爾為收發器開發的專有介面,之后廣泛應用于類比、RF與其他元件。

英特爾與Xilinx都提到了設計模組化晶片時所面臨的一些挑戰。 CoWoS制程要求晶片的最大接面溫度維持在攝氏95度以下;Singh提到,DRAM堆疊每減少一層,溫度大約會提高兩度;Shumarayev則表示,英特爾要求晶片供應商為堆疊出貨的裸晶都是KGD (known good die),因為封裝壞晶粒的成本問題一直是多晶片封裝市場的困擾。

編譯:W. Lin;責編:Judith Cheng

參考原文:Hot Chips Spotlights Chip Stacks,by Rick Merritt

(文章來源:EET 電子工程專輯 )

關注行業動態,了解產業信息,以實現與時俱進,開拓創新,穩步發展。

標簽: 晶片 EMIB CCIX